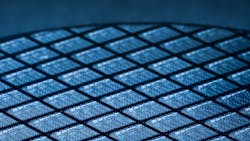

University Students Develop New Silicon Wafer Inspection Device

Download this article in PDF format.

As the global semiconductor shortage drags on, computer chip manufacturers are looking for new ways to make, inspect and distribute these hot commodities. A group of engineering students at the University of Colorado Boulder wants to help, and has come up with a new way for these chip makers to inspect their products and ensure that they’re ready for sale, distribution and use.

The team of mechanical engineering students developed a device that improves the inspection process. The Department of Mechanical Engineering seniors built a silicon wafer center-finding improvement device for KLA, a semiconductor manufacturing company. The school says that its senior design team’s prototype uses two cameras to capture the circular wafer’s edge, plus computer software to calculate the radius and find the wafer’s center.

Better Wafer Inspection Processes Wanted

According to SemiconductorEngineering, wafer inspection—or the science of finding defects on a wafer—is both challenging and costly. “This is due to process shrinks, design complexities and new materials,” it points out. “In addition, the ability to detect sub-30nm defects is challenging with today’s optical inspection tools.”

The idea is to find a defect of interest on a wafer. During the inspection process, a wafer inspection tool takes a photo of a die. Then, the tool takes a photo of another die and compares them. “If there’s a change, that’s generally a defect,” SemiconductorEngineering explains.

The complexities mount from there. For example, the inspection tool may detect defects on a wafer or a “nuisance,” the latter of which is an irregularity or false defect on the wafer (but not a defect that necessarily needs to be addressed).

“In the past, a tool could process the information and delineate the difference between the defects and nuisances on a map,” the publication adds. “But in more advanced nodes, the nuisances and defects appear to be bunched together on the map. And it’s becoming more difficult to distinguish the differences between the two.”

Answering the Call

With its wafer inspection project, the engineering team at UC Boulder says its goal was to find the wafer’s center to 10-micron accuracy in under two seconds. The center is the origin of a coordinate grid that is used to locate defects, it explains, and the test bench implements a custom algorithm and high-magnification cameras to inspect the wafer profile and log the center position.

“The reason this is important is that KLA has to inspect these wafers for defects, and when they find one, they need to know where on the wafer it is with a high-level of precision,” said Marty LaRocque, the team’s electro-mechanical engineer, in a university publication. “They have to establish a coordinate system on the wafer and the hardest part of that is finding the center.”

Currently, KLA is detecting the wafer’s center with 10 different images around the edge. The team of students designed its device to find the center just as efficiently with only two images. The team presented its silicon wafer center-finding improvement device at the College of Engineering and Applied Science Engineering Projects Expo 2022 in April.

Project Manager Jack Carver says that on one of KLA’s inspection tools, it currently takes the company eight seconds to align one wafer, and “we’re trying to get that down to two seconds,” he adds. “That 75% reduction would result in higher throughput at a time when silicon wafers are in short supply.”

About the Author

Bridget McCrea

Contributing Writer | Supply Chain Connect

Bridget McCrea is a freelance writer who covers business and technology for various publications.